TechSource Systems is MathWorks Authorised Reseller and Training Partner

Sign up for this introductory course the learn the basics of FPGA and Xilinx Vivado tools to get started for your project.

‘VHDL & FPGA Design Expert’ training is a comprehensive training course that comprises of 2 course modules: Designing with VHDL and Designing FPGAs Using the Vivado Design Suite 1. Based on Xilinx industry standard, this 6-day training package can be considered as the minimum training requirement for project readiness.

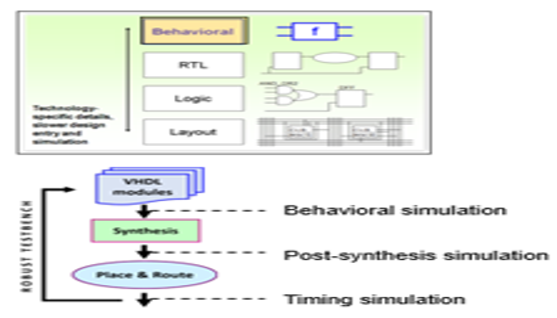

Designing with VHDL (3-day) provides a thorough introduction to the VHDL language. The emphasis is on writing efficient hardware designs, performing high-level HDL simulations, employing structural, register transfer level (RTL), and behavioral coding styles, targeting Xilinx devices specifically and FPGA devices in general, utilizing best coding practices.

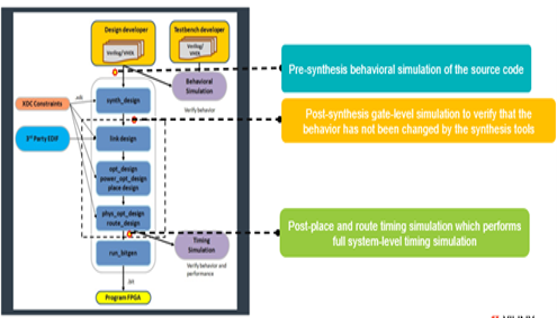

Designing FPGA Using the Vivado Design Suite 1 (2-day) offers introductory training on the Vivado® Design Suite and demonstrates the FPGA design flow for those uninitiated to FPGA design.

The course provides experience with creating a Vivado Design Suite project with source files, simulating a design, performing pin assignments, applying basic timing constraints, synthesizing and implementing, debugging a design, generating and downloading a bitstream onto a demo board.

Hands-on Project (1-day) on the last day allows you to test your knowledge and apply your skills immediately. No documentation, no labs instructions, you will face the real challenge to do a full FPGA design flow project with the guidance of our instructor.

Digital designers who are interested in FPGA design training and want to use VHDL effectively for modeling, design, and synthesis of digital designs and learn to use Xilinx FPGAs.

Basic digital design knowledge.

After completing this training, you will have the necessary skills to:

Designing with VHDL

FPGA Design Expert

TechSource Systems is MathWorks Authorised Reseller and Training Partner

Objective: Discusses the history of the VHDL language and provides an overview of the different features of VHDL.

Objective: Provides an overview of typical VHDL code, covering design units such as libraries, packages, entities, architectures, and configuration.

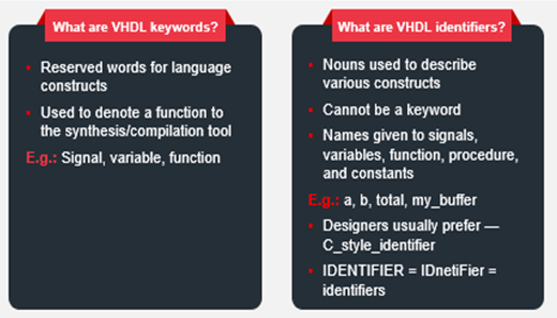

Objective: VHDL Objects, Keywords, Identifiers.

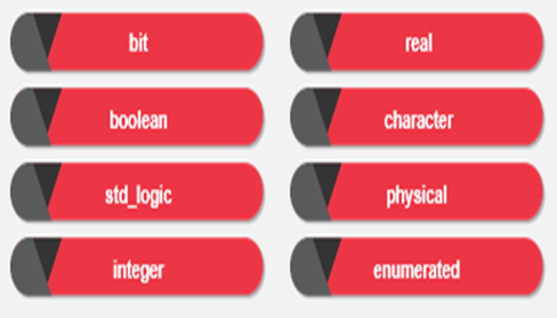

Objective: Covers both intrinsic and commonly used data types.

Objective: Covers composite data types (arrays and records).

Objective: Reviews all VHDL operator types.

Objective: Describes concurrent statements and how signals help in achieving concurrency.

Objective: Covers both conditional and unconditional assignments.

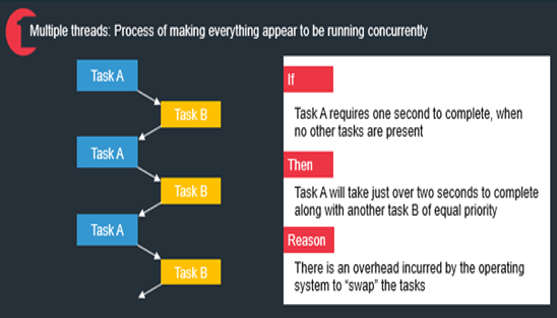

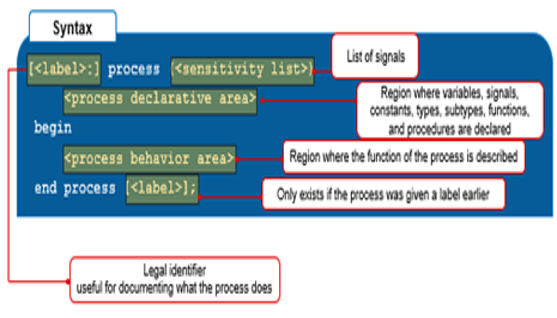

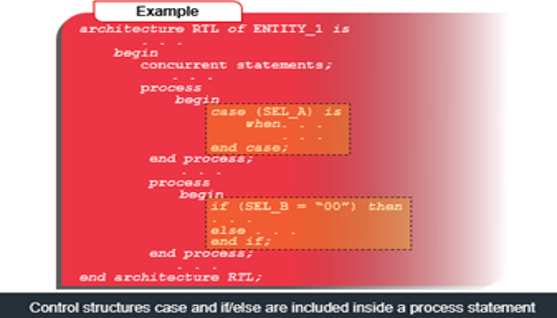

Objective: Introduces sequential programming techniques for a concurrent language. Variables are also discussed.

Objective: Covers both conditional and unconditional assignments.

Objective: Describes conditional statements such as if/else and case statements.

Objective: Introduces the concept of looping in both the simulation and synthesis environments.

Objective: Describes conditional statements such as if/else and case statements.

Objective: Introduces the concept of the VHDL testbench to verify the functionality of a design.

Objective: Describes the concept of VHDL assertions.

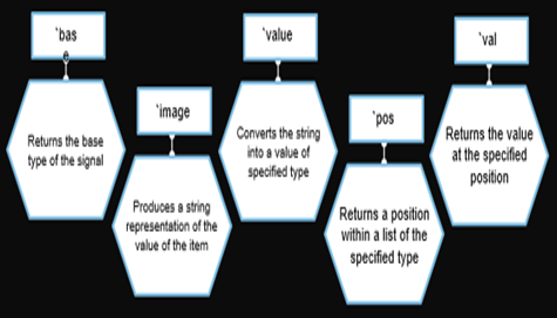

Objective: Describes attributes, both predefined and user defined.

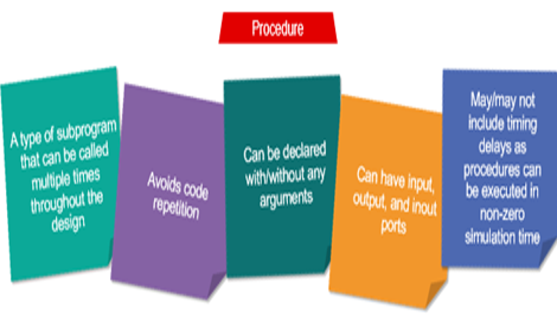

Objective: Covers the use of subprograms in verification and RTL code to model functional blocks.

Objective: Describes functions, which are integral to reusable and

maintainable code.

Objective: Describes procedures, common constructs that are also important for reusing and maintaining code.

Objective: Demonstrates how libraries and packages are declared and used.

Objective: Describes how to interact with a simulation via text I/O.

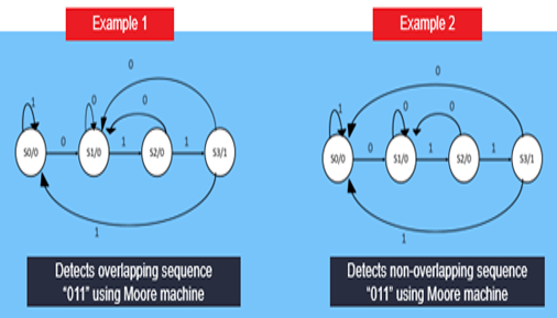

Objective: Provides an overview of finite state machines, one of the more commonly used circuits.

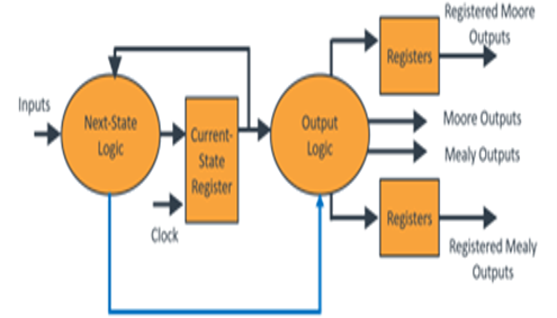

Objective: Describes how to implement a Mealy state machine in which the output is dependent on both the current state and the inputs.

Objective: Demonstrates how to implement a Moore state machine in which the output is dependent on the current state only.

Objective: Describes the guidelines and recommendations for using one or more procedural blocks when coding a finite state machine.

Objective: Introduces the Vivado simulator simulation environment. Race conditions are also discussed.

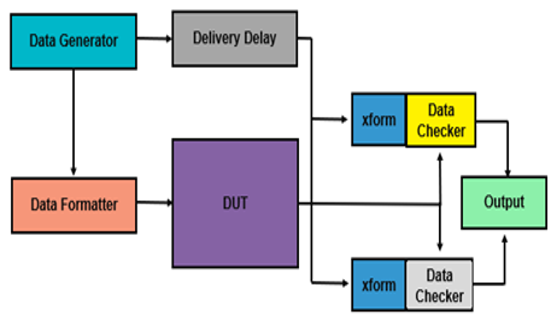

Objective: Explores how time-agnostic, self-checking testbenches can be written and applied.

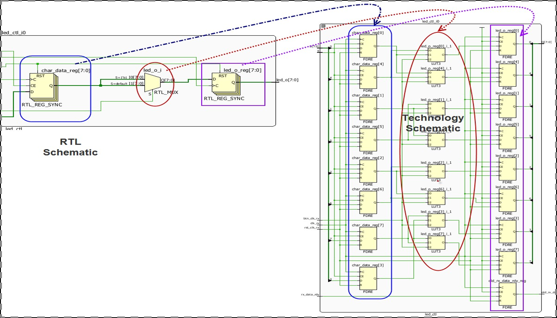

Objective: Focuses on Xilinx-specific implementation and chip-level optimization.

Objective: Overview of FPGA architecture, SSI technology, and SoC device architecture.

Objective: Introduces the methodology guidelines covered in this course and the UltraFast Design Methodology checklist.

Objective: Covers basic digital coding guidelines used in an FPGA design.

Objective: Introduces the Vivado design flows: the project flow and non-project batch flow.

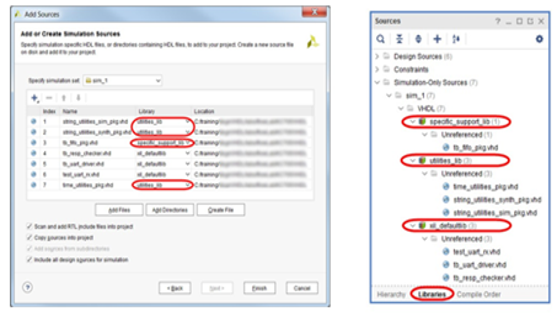

Objective: Introduces the project-based flow in the Vivado Design Suite: creating a project, adding files to the project, exploring the Vivado IDE, and simulating the design.

Objective: Generate and use Vivado timing reports to analyze failed timing paths.

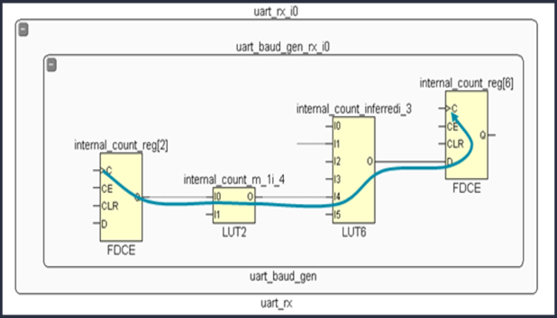

Objective: Describes the process of behavioral simulation and the simulation options available in the Vivado® IDE.

Objective: Estimate the amount of resources and default activity rates for a design and evaluate the estimated power calculated by XPE.

Objective: Create timing constraints according to the design scenario and synthesize and implement the design. Optionally, generate and download the bitstream to the demo board.

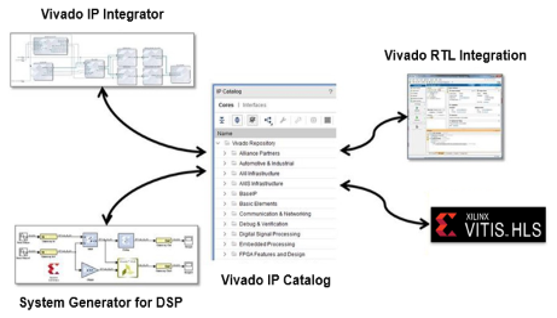

Objective: Customize IP, instantiate IP, and verify the hierarchy of your design IP.

Objective: Use the I/O Pin Planning layout to perform pin assignments in a design.

Objective: Apply clock constraints and perform timing analysis.

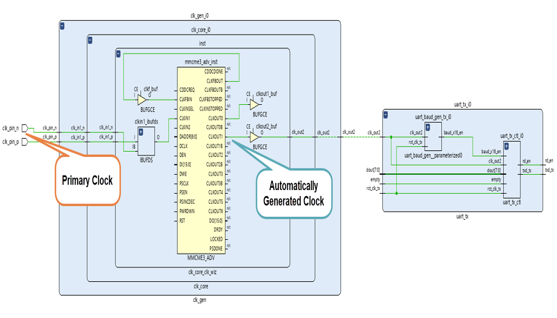

Objective: Use the report clock networks report to determine if there are any generated clocks in a design.

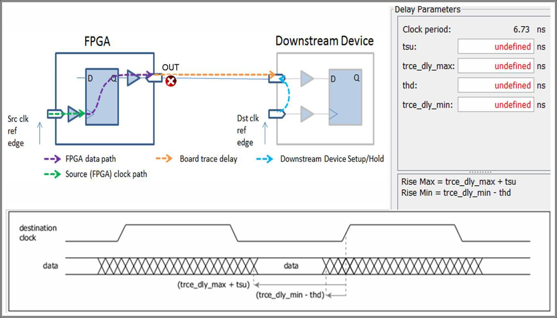

Objective: Apply I/O constraints and perform timing analysis.

Objective: Use the Timing Constraints Wizard to apply missing timing constraints in a design.

Objective: Describes the basics of clock gating and static timing analysis.

Objective: Reviews setup and hold timing calculations.

Objective: Describes how FPGAs can be configured.

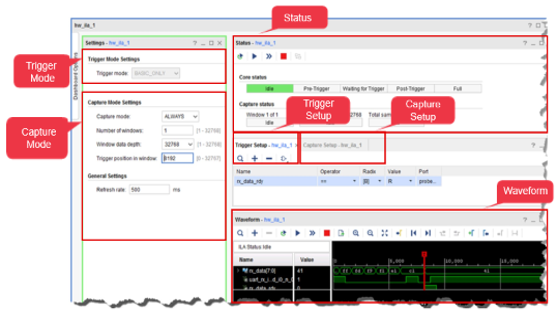

Objective: Overview of the Vivado logic analyzer for debugging a design.

Objective: Introduces the trigger capabilities of the Vivado logic analyzer.

Objective: Understand how the debug hub core is used to connect debug cores in a design.

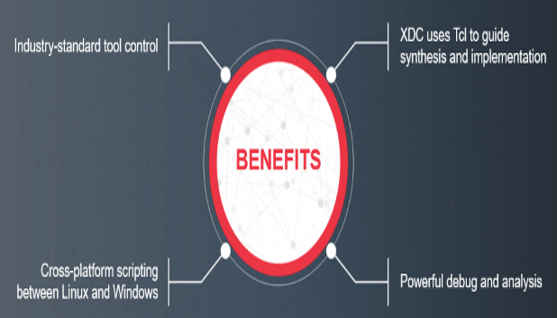

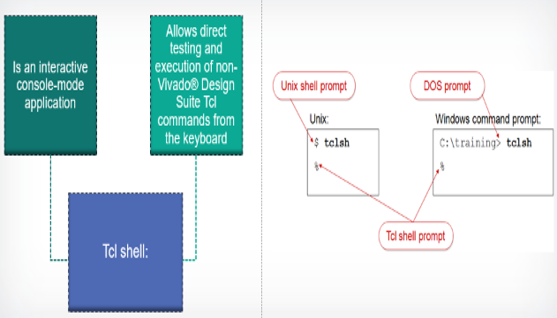

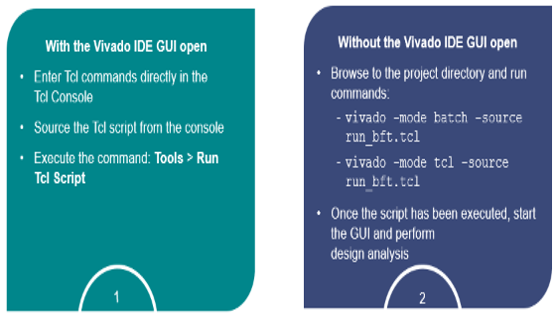

Objective: Introduces Tcl (tool command language).

Objective: Understand the Tcl syntax and structure.

Objective: Explains what Tcl commands are executed in a Vivado Design Suite project flow.

FPGA Design Flow Hands-on practices.