TechSource Systems is MathWorks Authorised Reseller and Training Partner

Introduces designers to the basic concepts of high-speed memory I/O design,

implementation, and debugging using Xilinx 7 series FPGAs.

This two-day course teaches hardware designers who are new to high-speed memory I/O to design a memory interface in Xilinx FPGAs. It introduces designers to the basic concepts of high-speed memory I/O design, implementation, and debugging using Xilinx 7 series FPGAs.

Additionally, students will learn about the tools available for high-speed memory interface design, debug and implementation of high-speed memory interfaces.

The major memory types covered are DDR2 and DDR3. The following memory types are covered on demand: RLDRAMII, LPDDR2, and QDRII+. Labs are available for DDR3 on the Kintex®-7 FPGA KC705 board.

FPGA designers and logic designers.

Helpful/nice to have:

After completing this comprehensive training, you will know how to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

Objective: describes all of the features in the Xilinx® 7 series FPGAs. It also describes the dedicated IP, subfamilies, and available evaluation kits of the 7 series FPGAs.

Objective: provides an overview of memory devices.

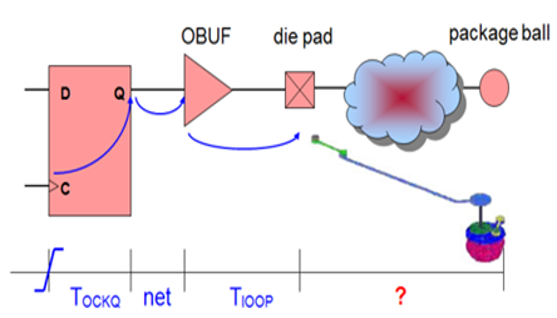

Objective: explains all the resources required for memory interfaces in Xilinx® 7 series FPGAs.

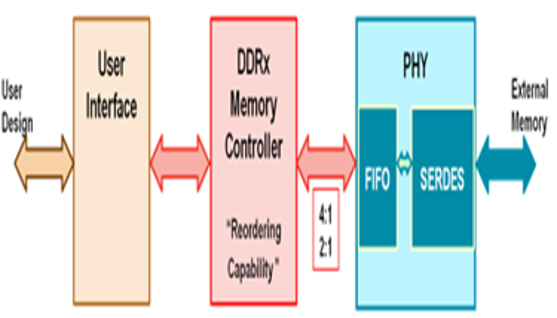

Objective: explains architectural and functional details of the memory controllers in Xilinx® 7 series FPGAs.

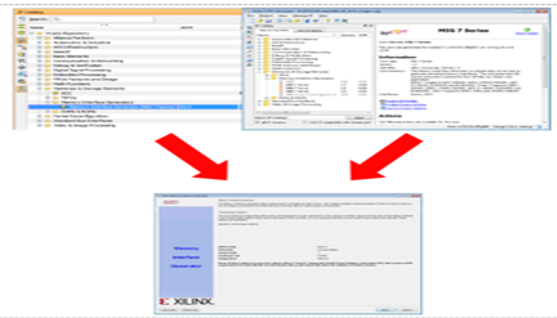

Objective: explains using the Memory Interface Generator (MIG) tool.

Objective: explains the simulation options for Memory Interface Generator (MIG) tool designs.

Objective: explains the implementation options for Memory Interface Generator (MIG) tool designs.

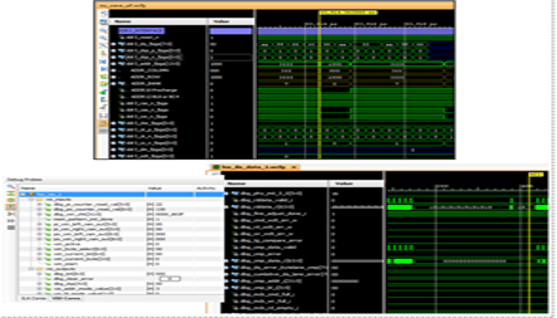

Objective: discusses test and debugging options for Memory Interface Generator (MIG) tool designs.

Objective: discusses test the usage of the Memory Interface Generator (MIG) tool in embedded designs.

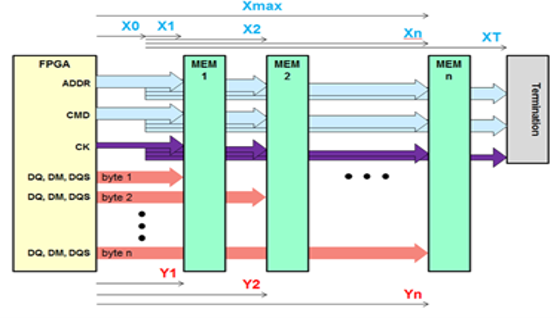

Objective: explains the board-level design requirements and options for Memory Interface Generator (MIG) tool designs.

Objective: explains the PCB simulation options for Memory Interface Generator (MIG) tool designs.