TechSource Systems is MathWorks Authorised Reseller and Training Partner

Learn DSP fundamentals from the perspective of implementation within the FPGA fabric

Complimentary Services: Post training email support & 1-hr consultation session within 1 month after the course completion!

This three-day course will review DSP fundamentals from the perspective of implementation within the FPGA fabric. Particular emphasis will be given to highlighting the cost, with respect to both resources and performance, associated with the implementation of various DSP techniques and algorithms. Topics include:

Engineers who wants to implement various DSP algorithms/techniques within FPGA fabric.

MATLAB Fundamentals and Simulink for System and Algorithm Modeling.

Upon the completion of this training, attendee will be able to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

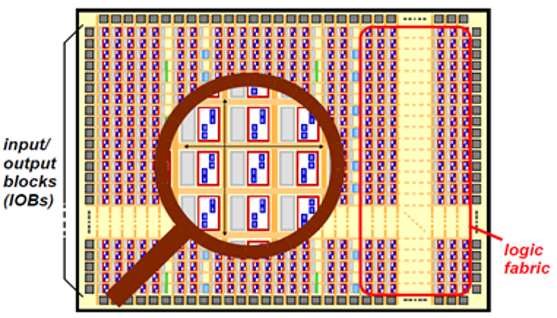

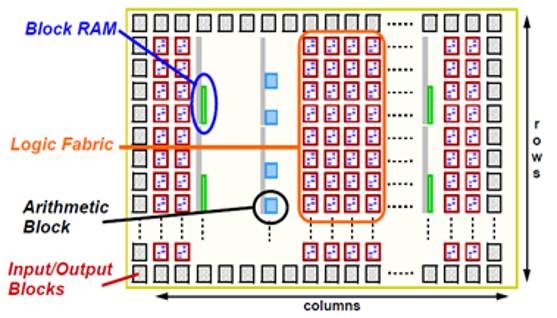

Objective: Provide introduction to DSP and FPGA. Understand general FPGA architecture and why FPGAs are uniquely suited to the implementation of DSP algorithms.

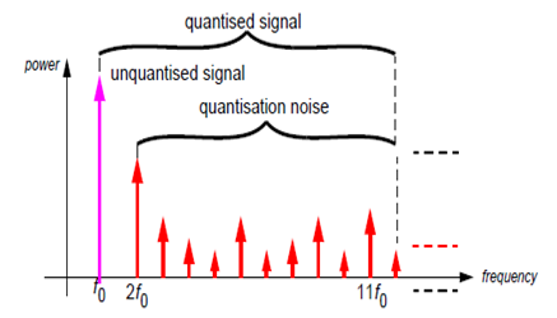

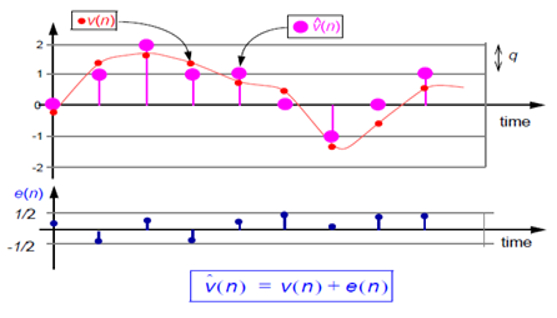

Objective: Review fundamental concepts of sampling theorem, quantization, Fourier analysis and digital filter design.

Objective: Explore different Xilinx FPGA families and architectures. Provide introduction to Spartan 3 and Virtex-5 FPGAs.

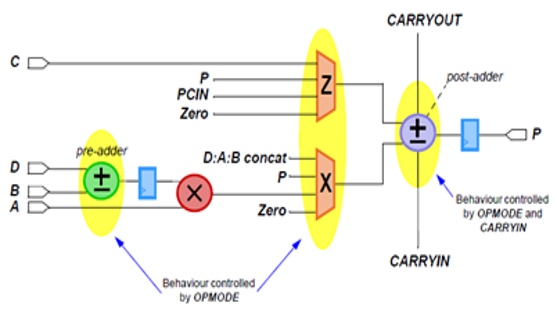

Objective: Understand DSP slices, clocking resources and power consumption.

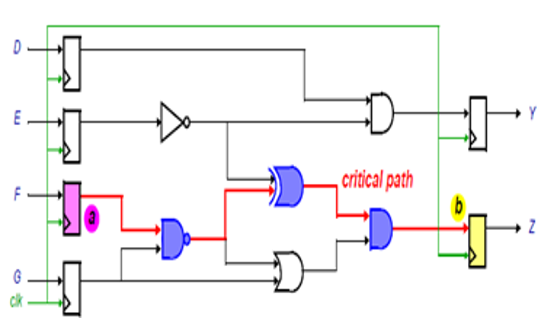

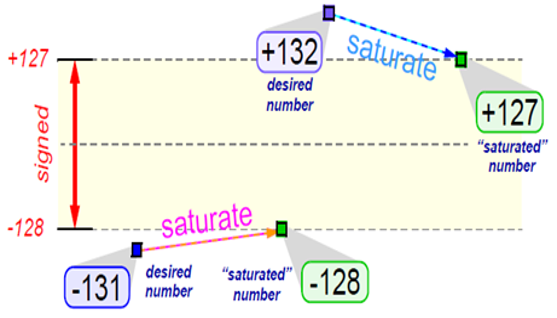

Objective: Understand fixed point binary arithmetic. Map arithmetic operations to Xilinx FPGA hardware.

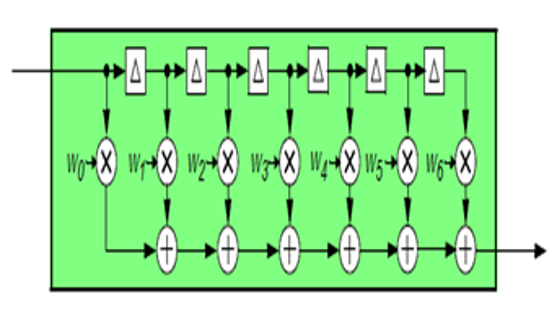

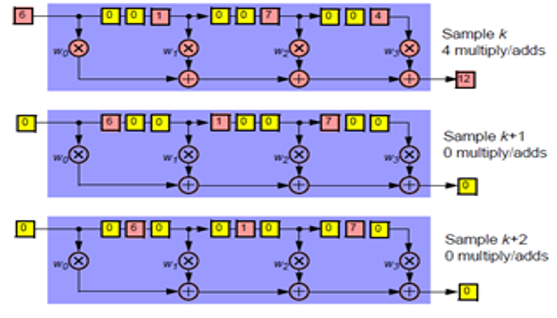

Objective: Review the representation of DSP algorithms using signal flow graph. Use the Cut Set method to improve timing performance. Implement parallel and serial FIR filters.

Objective: Discuss the theory and FPGA implementation of the Fast Fourier Transform.

Objective: Develop polyphase structure for efficient implementation of multirate filters. Use CIC filter for interpolation and decimation.

Objective: Introduce CORDIC algorithm for calculation of various trigonometric functions.

Objective: Introduce LMS algorithm in adaptive signal processing. Illustrate QR algorithm as a Recursive Least Squares (RLS) technique and why it is particularly suited to FPGA implementation.

Objective: Review quadrature modulation and pulse-shaping. Discuss implementation of numerically controlled oscillators.

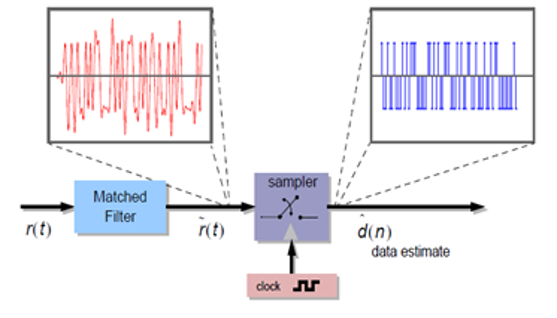

Objective: Cover symbol timing recovery, carrier phase recovery, carrier frequency recovery and frame synchronization.