Course

Highlights

This three-days hands-on training will provide experience in applying Signal and Image Processing with the Vitis Model Composer tool for model-based designs.

The course provides experience with:

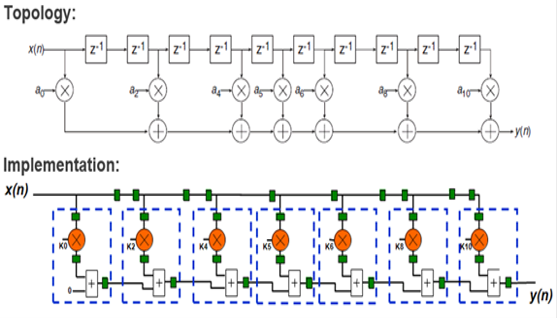

- Working on variety of filter techniques with emphasis on optimal implementation in AMD Xilinx devices followed by examination of FFTs, Video and Image Processing

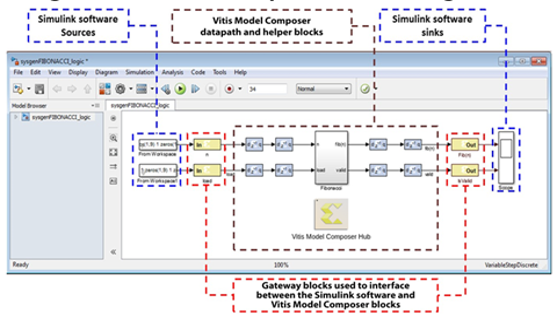

- Creating a model-based design using HDL, HLS, and AIE library blocks along with custom blocks in Vitis Model Composer

- Implementing DSP functions using Vitis Model Composer

- Utilizing design implementation tools

- Transforming algorithmic specifications to production-quality IP implementations using automatic optimizations and leveraging the high-level synthesis technology of the Vitis HLS tool

- Creating Versal® AI Engine graphs and kernels using Vitis Model Composer

- Connecting AI Engine blocks and non-AI Engine blocks

- Verifying and debugging AI Engine code using the Vitis analyzer

- Simulating and debugging a complex system created using AI Engine library blocks

Who Should

Attend

System engineers, system designers, logic designers, and experienced hardware engineers who are implementing Versal AI Engine, HDL and HLS algorithms using the MathWorks MATLAB® and Simulink® software and want to use Vitis Model Composer.

Course

Prerequisites

- Basic experience with the MATLAB and Simulink software

- Basic understanding of DSP designs and sampling theory

- Comfort with the C/C++ programming language for HLS or AI Engine model designs

Course

Benefits

Upon the completion of the course, the participants will be able to:

- Utilize fixed point binary arithmetic and identify how to use this knowledge to create efficient designs in FPGAs

- Recognize how both the CLB slices in FPGAs and the more advanced DSP48s are used to implement DSP algorithms

- Explain the dataflow through the device and how to use distributed memory, block RAM, registers, and SRLs to properly implement these designs

- Construct different FIR filter and FFT implementations and how to optimize these implementations in the FPGA

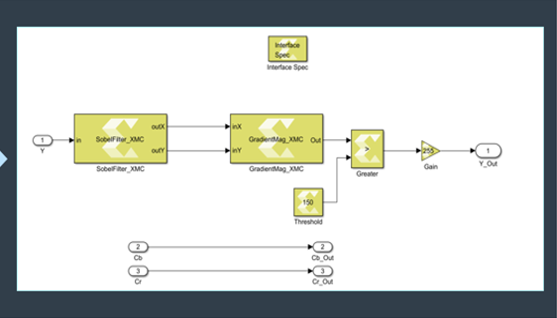

- Explain the algorithms for video and imaging systems and their implementations in FPGAs

- Use optimized HDL, HLS, and AI Engine blocks directly from the Simulink tool library browser

- Create, simulate, and debug a Vitis Model Composer design in the Simulink Environment using HDL, HLS, and AIE block libraries

- Perform co-simulation and hardware verification

- Use DSP blocks in Vitis Model Composer to implement DSP functions

- Implement multi-rate systems in Vitis Model Composer

- Design a processor-controllable interface using Vitis Model Composer

- Generate Ips from C-based design sources using the Vitis HLS tool for se in the Vitis Model Composer environment

- Import custom HDL, HLS and AI Engines code as blocks into Vitis Model Composer

- Generate output products using automatic code generation

- Connect AI Engine blocks and non-AI Engine blocks

- Perform AI Engine code verification using the Vitis analyzer

- Create, simulate, and debug a complex system created using AI Engine library blocks